有时候一句话就能改善高速信号的通道损耗???

发布时间:2023-09-18 16:46

作者:一博科技高速先生自媒体成员 黄刚

给大家一个思考的场景:当PCB设计完成,板材叠层确定,已经进入投板状态了,这时仿真评估发现高速信号通道裕量可能不保险,还有机会改善吗? 当然这个问题出现的概率不会很大啦,因为既然要进行仿真评估,那仿真验证的工作肯定会放在前面去,来提前判断通道的损耗是否ok,来确定是否使用更好的板材或者走更宽的走线来减小损耗。如果你真的遇到了一个设计完才开始仿真来进行损耗评估的SI工程师的话,高速先生可能都会为你感到悲伤哦!

但是要是你真的那么不走运,遇到了一个这样的仿真工程师,在你完成设计准备投板的时候告诉你高速信号的损耗裕量可能有点不够时,你还可以怎么办呢?这个时候叠层和板材早就确定好了,器件布局、走线都完成了,可能你需要重新推倒重新设计的概率已经超过了95%了,这个时候你看看这篇文章,有可能你就抓住剩下的5%的可能性,说简单的一句话就能改善本来不太够的损耗!

到底这篇文章想说怎么样的一个方法呢?我们先卖个关子哈。首先我们来看看我们PCB走线的损耗到底是由哪几大部分来决定的哈!

我们先从大方向来介绍PCB的损耗的分类。总体分为3种损耗:导体损耗,介质损耗和辐射损耗。大家可能听前两种比较多,实际情况下PCB的损耗也主要以前两种为主。至于辐射损耗,它也是和介电常数DK相关的,另外辐射损耗基本只会在微带线存在,而且设计得当的话,可以把它降低到一个比较低的水平,在总的损耗里面占的比例非常小,这里不展开来介绍。

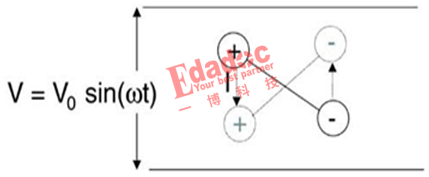

其中介质损耗主要由偶极子的极化现象所产生的,为了大家不喜欢听太多理论的习惯出发,我们把理论长话短说,就好像下图一样,施加电压频率越高,那么电流就越大,材料中发生摆动的偶极子数越多,在电场作用下偶极子移动量越大,同时体电阻率越大,介质中的功率损耗也就越高了。为了描述这个度量偶极子运动规律的材料特性,DF这个概念就应运而生了。

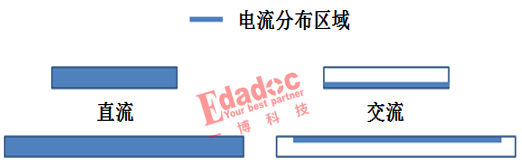

再说说另外一部分,导体损耗的原理。首先必须知道高速理论中有一个重要的概念,叫做趋肤效应,在较高频时电流会沿着导体的表面来运行,也就是在高频的时候,我们电阻的大小取决于电流流过的横截面大小,电流流经的横截面越小,电阻越大,因此导体损耗也是随着频率的升高而逐渐增大。

对不起,高速先生已经尽力去压缩理论知识了,可能还会有部分粉丝觉得不需要,但是这个对于大家如何去分析PCB走线的损耗还是有很大的帮助哈! 总结一下上面所说到的损耗因素,就是板材主要决定了介质损耗,也就是我们常说的板材DF的大小对损耗的影响是最大的,也正是因为这个原因我们区分出了不同等级的板材。另外走线的线宽和铜厚影响着导体损耗。上面说的和我们摘要的场景是很符合的,板材定了,基本上介质损耗定了,叠层和设计定了,走线的结构定了,导体损耗也基本上定了。那么如果在这种情况下还想改善损耗的话,我们就必须看看到底还有没有什么因素能够影响我们的损耗了。

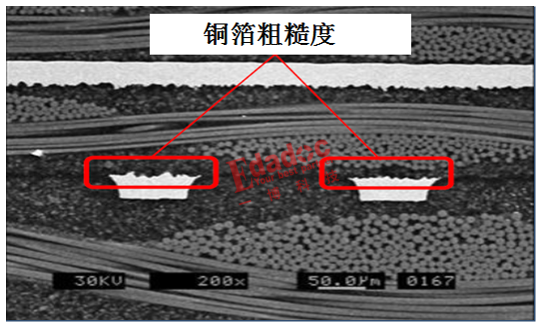

其实看到我们高速先生文章或者我们新推出的书籍的粉丝就会知道,除了上面的因素外,我们还介绍了铜箔粗糙度的影响。铜箔表面是比较粗糙的(为了增加铜箔和PP的粘结性),所以高速需要考虑铜箔粗糙度,而铜箔粗糙的程度也会影响走线的损耗。

其实这个损耗也可以算在导体损耗里面去,原理大概是这样的,由于有趋肤效应,电流会在铜牙上传输,经过突起的铜牙时,相较于平滑的铜面,电流的传输路径变长了,因此又会进一步同时增加直流和交流电阻,从而增加导体损耗。

我们熟知的几种不同粗糙度等级类型的铜箔包括了普通STD铜箔,RTF反转铜箔和HVLP超低轮廓铜箔,当然现在还有在HVLP铜箔基础上继续优化的HVLP2和HVLP3铜箔了。但是现实是这样的,很多朋友知道了不同的粗糙度的铜箔会影响损耗,但是不知道到底有多大的影响,能不能有定量的数据来给出。大家其实想一想都觉得不容易,不容易的点主要是损耗是由几个大的部分共同组成的,主要包括了板材DF、走线宽度和铜厚、参考层厚度以及现在说的铜箔粗糙度。如果你想单独提取出不同类型的铜箔粗糙度的影响,那你就必须保证其中的因素是一致的才能单纯的提取出来。说具体点也就是要保证板材一样,走线结构一样,走线参考的厚度也一样的情况下,只是铜箔粗糙度不一样才能单独知道铜箔粗糙度的影响。大家觉得有可能做到吗?

当然,高速先生既然问出来,说明高速先生肯定已经做到了哈!高速先生为此也专门制作了一块测试板,为的就是对比下现在很流行的RTF和HVLP铜箔的差异。对,单纯是铜箔不一样带来的差异!

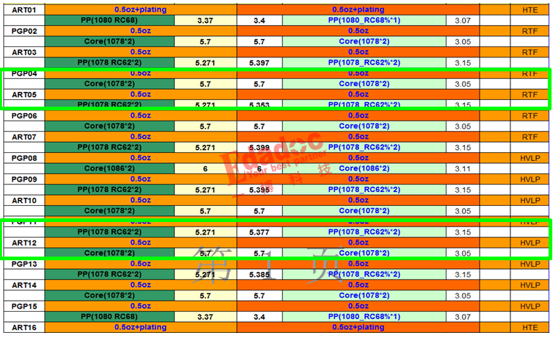

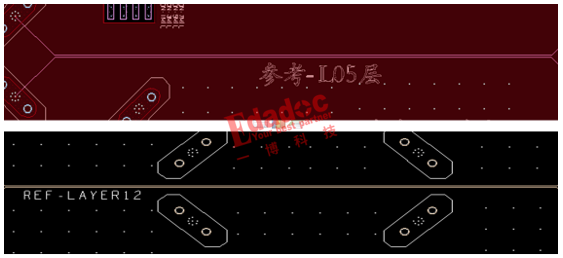

高速先生在同一个叠层里上下部分分别去做HVLP和RTF铜箔,由于上下部分是对称的,因此走线结构和介质厚度完全相同,另外同一个叠层的话就表示板材一样,也是同一次加工,不会产生加工误差,因为分别在指定的RTF和HVLP铜箔的走线层走一样长度的走线,就能够成功做到这一点啦!

就像这块测试板一样,我们在L5层和L12层分别走RTF和HVLP铜箔的走线,走线长度一致(去嵌后走线长度为3inch),因此除了铜箔粗糙度不一样,其他因素都能保证相同,这样的话进行这两对走线的测试,就能够很纯粹的对比得到两种不同铜箔粗糙度对损耗的影响了。

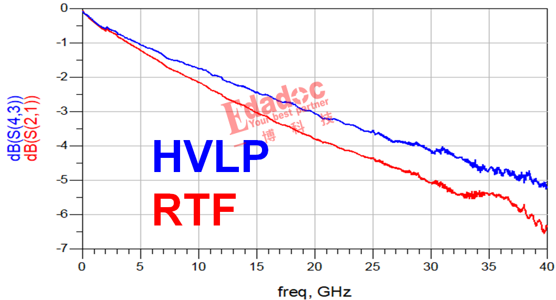

恩,话不多说,我们立马给出测试出来的损耗差异,如下所示:从损耗的结果来看,RTF铜箔的确会比HVLP铜箔要差(这个大家都知道了)。而从定量的结果来分析,单纯铜箔粗糙度对损耗的影响来到了15%-20%的程度,算是一个很大的影响因素了。

本篇文章算是比较长的文章了,首先我们从理论上给大家分析了造成PCB损耗的几个大的因素。然后我们给大家分享了一种如何单独提取出不同铜箔粗糙度对损耗的影响的测试方法,从而定量的得到了不同粗糙度对走线损耗的影响程度。

好了,说了半天回答下刚开始场景的问题了,有没有可能在设计和板材叠层都不变的情况下一句话改善损耗的方法呢?有的等级的板材可能会配有多种粗糙度类型的铜箔,而且如果不明显提出的话,标配是比较low的类型,这时候在工程确认的时候如果大家想换成好的铜箔不就是一句话就能够搞掂了吗!